Un processeur qui perd le nord

Retour trois années en arrière quand je me penchais sur la gestion du stockage de masse d'un projet professionnel. C'est toujours avec le fameux processeur 8148 de Texas Instrument, le même projet que pour l'épisode 1.

Le stockage de masse est assuré par une mémoire flash NOR. En réalité l'implémentation n'était pas le principal problème, je vais raconter à nouveau un bogue assez délicat à identifier.

Mais d'abord, contexte !

Contexte

Choix de la mémoire

Donc sur ce projet, comme tout projet avec un système embarqué, se pose la question du stockage du système d'exploitation, des données et de comment charger le tout.

Il y a en général plusieurs possibilités pour un tel système : une mémoire NAND, NOR, une carte SD, une mémoire eMMC (une carte SD soudée), une clé USB voire via Internet. Bien entendu, chaque support a son lot d'avantages et inconvénients, voici pourquoi le NOR a été choisi :

- Il est très fiable sur la durée (bien plus que les flashs NAND ou les mémoires SD/eMMC) ;

- Sa lenteur n'était pas impactant pour notre système (c'est en effet de tous la méthode d'accès la plus lente) ;

- Son espace de stockage (256 Mio) pour son prix était suffisant, sachant que la NOR est plus cher au Gio que les autres dispositifs ;

- Il est possible d'exécuter le système en place (c'est le mécanisme XIP pour eXecute In Place) ce qui économise de la RAM et simplifie la conception.

Le dernier point est une propriété intéressante. En fait le processeur est capable d'adresser directement dans la mémoire NOR, les instructions machine du genre exécuter la fonction de cette adresse n'a pas besoin d'être chargé en RAM, le processeur peut accéder à cette adresse depuis la NOR et exécuter la dite fonction sans charger le code au préalable.

Préparation

Cependant, la dite technique XIP nécessite d'être précautionneux. Tout d'abord, le processeur au départ n'a pas accès à tout l'espace de stockage que propose notre mémoire.

Car dans le monde ARM (ce qui suit reste plus ou moins valable avec d'autres architectures, potentiellement avec d'autres noms), quand nous appuyons sur le bouton d'alimentation de la carte, l'alimentation démarre le processeur qui lance un petit chargeur de démarrage située dans sa ROM et qui a été conçu par le fabricant de la puce, ici Texas Instrument. Il va initialiser le minimum nécessaire dans le SoC et essayer de charger du code depuis un espace de stockage (notre mémoire NOR bien entendu ici, mais cela peut être par Ethernet, USB, mémoire NAND, carte SD ou autre). Dans notre cas, nous avons configuré (matériellement, en mettant des pins du processeur à 1 et d'autres à 0) de sorte que ce chargeur de démarrage cherche notre système sur la carte SD (car durant le développement, nous avons une carte SD), et si rien n'est trouvé, charger depuis la NOR.

Ce sont des mécanismes assez simples derrière. Pour le démarrage SD, le processeur détecte si une carte est présente, essaye de trouver un fichier nommé MLO dans un système de fichier FAT de la première partition pour le charger. Pour la NOR, il vérifie si les 4 premiers octets (situés à l'adresse 0x08000000) sont non nuls (donc différents de 0xFFFFFFFF ou 0x00000000). Si le chargement est effectué mais que cela n'aboutit sur rien, le processeur sera bloqué. Donc il faut veiller à charger quelque chose de correct.

Et pour charger le code initial (dans notre cas notre propre chargeur de démarrage U-boot, qui chargera Linux, qui chargera le reste des applications), le chargeur de démarrage de Texas Instrument n'a pas besoin de tout charger. Essentiellement car c'est plus simple, mais aussi parce que c'est plus générique, toute mémoire NOR pourra être chargée à priori quelque soit sa taille réelle.

Donc il ne charge que les 4 premiers kiloctets disponibles. Ces premières instructions de U-boot vont servir principalement à initialiser le nécessaire pour accéder au reste de la mémoire NOR, initialiser également la pile, la vitesse du processeur, etc.

C'est pour cela que nous avons le code suivant situé dans les 4 premiers kiloctets. Puis il y a une subtilité technique à prendre en compte. Nous allons changer les paramètres d'accès à la mémoire NOR. Cela se fait par l'écriture sur 7 registres différents dans le processeur. Non seulement nous allons dire au processeur d'activer des lignes d'adresses supplémentaires (permettant l'accès à toute la mémoire disponible), mais en plus nous allons modifier la vitesse d'accès pour améliorer les performances globales.

Les paramètres d'accès à la NOR sont situés dans les registres GPMC (adresses 0x51000060 à 0x51000078). Nous pouvons indiquer au processeur, pour chaque caractéristique du signal pour dialoguer avec la NOR, le nombre de cycles d'horloge nécessaires. Ces valeurs dépendent donc de la vitesse d'un cycle d'horloge et des caractéristiques de la mémoire NOR.

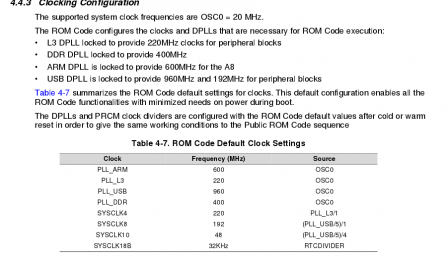

Attention, quand je parle de la vitesse d'un cycle d'horloge, ce n'est pas

directement celui du processeur lui même. En général au sein d'un circuit, il y

a une chaîne d'horloge qui se met en place pour alimenter chaque sous-système

avec une vitesse qui lui convient. Ainsi le réseau, le multimédia, l'USB, le

PCIe ou le processeur lui même ont des horloges propres. Ces horloges sont

construits à partir de quartz qui générèrent un signal entre 15 et 25 MHz.

Ensuite une PLL va amplifier ce signal pour moduler sa vitesse afin d'atteindre

parfois plusieurs GHz. Dans notre cas, le quartz OSC0 (à 20 MHz) alimente la

DPLL L3 (jusqu'à 220 MHz) qui alimente l'horloge GPMC qui divise par quatre le

signal précédent (jusqu'à 55 MHz donc). Je ferais sans doute un article complet

sur le sujet des horloges.

Et comme nous allons changer la vitesse d'accès à la mémoire, alors que nous exécutons le code depuis la NOR elle même, vous pouvez deviner un problème. Entre le changement du premier et du dernier registre, les temps d'accès à la NOR ne seront plus cohérents, le système va se bloquer faute de pouvoir lire les instructions suivantes. Du coup il est nécessaire de copier le bout de code qui fait ce changement dans la SRAM (une petite zone de mémoire interne au processeur à l'adresse 0x40400000, qui n'est pas impactée par nos changements) afin de l'exécuter depuis celle-ci avant de revenir exécuter le code dans la NOR une fois l'opération faite.

Cela est fait via les lignes suivantes (l'essentiel du code employé provient du code de Texas Instrument qu'il a fallu adapter à notre cas) :

/**************************************************************************

* cpy_nor_gpmc_code: relocates nor gpmc init code into ocmc0 where its

* safer to execute

* R2 is loaded wtih size of data to be copied, this should be calculated

* if we are modifying nor_gpmc_init()

*************************************************************************/

.global cpy_nor_gpmc_code

cpy_nor_gpmc_code:

stmfd sp!, {r0 - r10}

/* Copy NOR GPMC init code into SRAM */

adr r0, nor_gpmc_init /* get addr of nor gpmc init code */

mov r2, #640 /* r2 <- copy size(% by 32 bytes:r3-r10 (8) regs used) */

ldr r1, sram_pc_start /* r1 <- dest address (passed in) */

add r2, r2, r0 /* r2 <- source end address */

next2:

ldmia r0!, {r3 - r10} /* copy from source address r0 */

stmia r1!, {r3 - r10} /* copy to target address r1 */

cmp r0, r2 /* until source end address r2 */

bne next2

ldmfd sp!, {r0 - r10}

mov pc, lr /* back to caller */

Ce code fonctionne comme attendu, les premières cartes venant de la série A fonctionnent tous sans encombres.

Les problèmes arrivent

Quelques mois plus tard, un second jeu de cartes électroniques arrive avec une révision matérielle pour corriger les premiers défauts relevés. Et au bout de quelques heures, nous détectons un problème fondamental : sur certaines de ces cartes, le démarrage depuis la NOR ne fonctionne pas du tout, sur d'autres c'est aléatoire (de 1 fois sur 2 à 1 fois sur 100) et sur un exemplaire, aucun problème.

C'est pourtant, à ce stade, le même code qui est exécuté que sur les premières cartes qui ne bronchent toujours pas dans cet exercice. Notons également que sur ces nouvelles cartes, le démarrage depuis une carte SD ne pose aucun problème. D'ailleurs charger U-boot depuis la carte SD et le reste depuis la NOR ne présente aucun problème non plus.

La première piste est évidemment de vérifier tous mes calculs pour les registres d'accès à la NOR. Nous tombons tous d'accord sur le fait que ces valeurs sont correctes. Nous vérifions également l'ensemble des changements matériels autour du processeur et de la NOR et il n'y a rien. Tout au mieux, le responsable du routage de la carte (celui qui est responsable de transformer les liaisons logiques entre les composants en un circuit avec les pistes dessinées sur le plan final) note une différence de quelques micro/millimètres sur la longueur de ces fils entre les deux versions.

Mais rien de très intéressant, le module n'a pas beaucoup bougé sur ces fonctions et pourtant, le comportement est aléatoire. Nous prenons donc la JTAG pour en savoir plus afin de voir à quel endroit le démarrage échoue. Sur la plupart des modèles, cela tourne autour des registres du Watchdog. Mais si on supprime cette section du code, cela apparaît plus loin. Il semble donc que les échecs se produisent autour d'un certain nombre d'instructions constant depuis le démarrage plutôt que sur une instruction particulière. La JTAG nous montre que à l'instruction de trop, il va charger l'instruction suivante à une adresse délirante avant de retomber sur le vecteur d'exceptions du processeur pour avoir accédé dans une zone mémoire invalide.

Pour essayer d'identifier la cause de l'échec, le concepteur de la carte prend son oscilloscope à bras le corps et fait les mesures pendant que j'exécute le logiciel avec la JTAG pas à pas. Il semble que par moment le processeur fasse des signaux d'accès à la NOR d'environ 10 nanosecondes (oui, nanosecondes) trop courts. Pourtant les valeurs des registres que nous avons indiqué sont bons.

La solution

Une première solution est d'abaisser significativement les performances d'accès à la NOR et cela semble fonctionner. Mais si la NOR n'était pas un soucis niveau performances, nous avons une exigence contractuelle de démarrer l'ensemble du système en moins d'une minute. Et avec ces réglages, ce n'était plus possible. Puis nous ne comprenons toujours pas la cause du problème ce qui est gênant.

Il me faudra près d'une semaine de recherche dans la documentation de Texas Instrument pour comprendre la cause du problème et ainsi comment le résoudre. Je tombe en effet sur l'information suivante (page 1027 du document technique de référence) :

Or, si on prend le document de référence condensé page 183, on a :

Vous ne voyez pas ? Il y a pourtant une incohérence pour une source d'horloge : la DPLL L3 qui est pour l'OPP 100 de 220 MHz et de l'autre de 200 MHz.

Or, tous mes calculs ont été conçus pour un signal d'entrée de 50 MHz et non de 55 MHz, ce qui donne un temps d'accès par cycle respectivement de 18 à 20 nanosecondes, soit bien sûr 2 nanosecondes d'écart. Quand on sait que la quasi-totalité de la configuration du signal d'accès tourne autour de 4 à 6 cycles par élément du signal, on retombe sur les 10 nanosecondes environ plus court constatés plus haut.

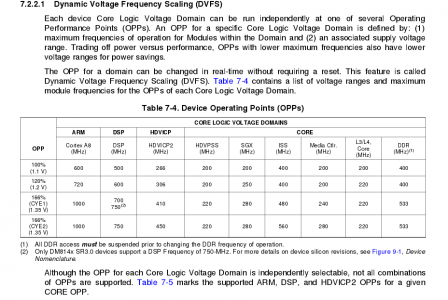

En quoi la documentation / implémentation de Texas Instrument est étrange ? En fait il faut expliquer brièvement ce qu'est un OPP. Un OPP pour OPerating Point est une méthode pour gérer l'énergie. Il consiste à fixer les fréquences maximales des différentes horloges du système par rapport à la tension d'alimentation du processeur. Plus le processeur consomme d'énergie (avec une tension élevée), plus les fréquences peuvent être élevées, mais plus la température peut monter également. En général on utilise le terme Dynamic Voltage Frequency Scaling pour décrire ce mécanisme.

Ce qui est curieux est que lors du démarrage NOR, par défaut, la ROM de Texas Instrument utilise l'OPP100 (celui de base) pour toutes les fréquences... sauf la L3 dont on se sert où c'est un OPP120 qui est employé. Cela n'est pas très cohérent comme choix et c'est ce qui nous a induit en erreur dans les calculs. Dans notre cas, pour éviter d'avoir besoin d'une ventilation active de la chaleur, nous souhaitons avoir une OPP100 durant le fonctionnement de l'appareil.

Pourquoi ce caractère aléatoire ?

Jusqu'ici j'ai expliqué le cadre général, l'origine du bogue a été trouvée, mais je n'ai pas expliqué pourquoi sur certaines cartes cela fonctionne, d'autres pas. Pourtant le code et le problème devrait se manifester partout.

Tout d'abord le démarrage SD fonctionne car dans U-boot, je changeais manuellement la fréquence des différentes horloges pour fixer le tout à l'OPP100 (et pour démarrer certaines horloges pour le processeur multimédia dont j'ai parlé dans le précédent article, chose qui n'est pas fait par le chargeur de démarrage de Texas Instrument). Du coup je supprimais le problème dans ce cas.

Le caractère aléatoire vient des différences minimes entre les différentes cartes. Comme je l'ai dit plus haut, les nouveaux modèles étaient plus sensibles à cause de la longueur des pistes qui avait changé, mais aussi parce que les composants ne sont pas identiques (numéros de série différentes, modèles différents pour les quartz, etc.). Étant donné la différence minime dans les temps d'accès, ces variations mineurs en temps normal peuvent avoir des impacts importants sur la longue.

D'autant que je changeais les fréquences d'horloge peu après la configuration du GPMC. Du coup, certains modèles avaient parfois la possibilité de régler le problème en abaissant la fréquence d'horloge finale en accédant à ces instructions à temps et sans encombre, d'autres pas.

Conclusion

Nous avons pu voir un problème qui survient parfois dans le domaine, des cartes qui se comportent différemment. Cela montre la nécessité de tester chaque modèle même si à priori c'est le même code, le même circuit. Chaque carte est unique. Il est nécessaire de documenter au maximum les petits changements qui peuvent être opérés. une collaboration forte entre l'équipe matérielle et logicielle est également fondamentale, il est probable que la cause n'aurait pas été retrouvée si vite sans cela. Chaque équipe ayant pu apporter des informations cruciales dans la résolution du problème.

Ensuite, bien entendu, la lecture de la documentation est importante, il faut tout vérifier, tout contrôler. Même ce qui paraît évident / logique. Il aurait été aussi appréciable que Texas Instrument choisisse une voie de moindre surprise en adoptant un choix cohérent dans les valeurs initiales de ses fréquences.

Et j'espère que vous aurez appris au sujet du démarrage sur les plateformes

ARM et de la gestion des horloges.